## **Datasheet: LTE Single Channel FDMA**

#### Features

- **Sample Rates**: Very high clock speeds, e.g., as high as 450MHz in 65nm FPGA technology (highest commercially available FPGA-based throughputs)

- Performance: 41/200% faster than Xilinx/Intel equivalents in computing resource blocks

- FFT size: 35 transforms sizes required by LTE SC-FDMA, 12 points to 1296 points

- Dynamic Range: combined block floating point and floating point architecture means smaller word lengths can be used for post-processing operations such as equalization (~6db/bit)

- **Scalability**: array based architecture means arbitrarily higher throughputs are obtained by increasing array size

- **Power**: array interconnects are entirely local, reducing parasitic routing capacitance to keep power dissipation low and clock speed high

- *Implementation FPGA*: Centar's DFT circuit can be used in any FPGA fabric containing embedded multipliers and memories

#### Usage

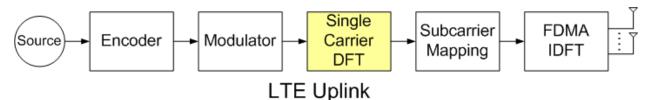

LTE Single Channel Frequency Division Multiple Access (LTE SC-FDMA):

## Options

- Fixed point word input lengths (2's complement)

- Output format

- Fixed-point

- Block floating-point

- Floating-point

## Algorithm

The transform computation is based on a new matrix formulation of the discreet Fourier transform<sup>1</sup> (DFT) which decomposes it into structured sets of *b*-point DFTs. This avoids the inherent irregularities of the usual signal flow graph approach which typically requires complex commutators or permutation circuits, variable memory blocks, large butterfly units, global interconnections, and stage-to-stage differences, all of which degrade performance and require extra logic resources. Centar's approach uses a small, regular, locally connected array, that

<sup>&</sup>lt;sup>1</sup> J. Greg Nash, "Computationally Efficient Systolic Array for Computing the Discreet Fourier Transform, IEEE Trans. Signal Processing, Vol. 53, No.12, December 2005, pp.4640-4641.

## CENTAR

keeps interconnect delays lower than cell delays, leading to high clock speeds/throughput and minimizes power. Because the circuit has a "memory based" architecture<sup>2</sup>, it is programmable so that the LTE SC-FDMA range of transforms can be performed on the same array. Finally, it includes a low overhead hybrid floating-point feature that increases dynamic range for a given fixed-point word size.

### Architecture

The architecture consists of a linear array of six pipelined, fine-grained, locally connected, simple processing elements, each containing a multiplier, a complex adder, a few registers and multiplexors. By cycling data through this array in a programmable way all 35 transform sizes can be supported. The actual size choices for transforms can be made at run-time.

Signal-to-Quantization-Noise-Ratio (SQNR)

Unlike traditional pipelined FFTs, an exponent is used in all addition and twiddle multiplication steps. Consequently, the SQNR is much higher than found in other FFT architectures for a given input bit length. Below are selected SQNR values for 5 different transform sizes.

|           | SC-FDMA Transform Sizes (12-bit input) |     |      |      |      |  |

|-----------|----------------------------------------|-----|------|------|------|--|

|           | 48                                     | 72  | 576  | 864  | 1200 |  |

| Mean      | 66                                     | 64  | 65   | 64   | 61   |  |

| Std. Dev. | 1.6                                    | 1.8 | 0.46 | 0.97 | 1.7  |  |

| Maximum   | 68                                     | 68  | 66   | 65   | 62   |  |

| Minimum   | 63                                     | 62  | 65   | 62   | 59   |  |

SQNR (db) (500 FFT blocks)

## **Detailed Transform Cycle Counts**

Total computational throughput in clock cycles per DFT are shown in the table below for each transform size. Typical clock speeds are greater than 400MHz, so the slowest throughput (N=1200-points) is ~9 $\mu$ sec. The speed can be scaled up by increasing the array size, so that with a x6 increase in size, the slowest throughput (*N*=1200-points) would be ~1.5 $\mu$ sec.

| DFT Size | Cycles per<br>DFT | DFT Size<br>N | Cycles per<br>DFT | DFT Size<br>N | Cycles per<br>DFT |

|----------|-------------------|---------------|-------------------|---------------|-------------------|

| 1296     | 2592              | 576           | 1154              | 180           | 365               |

| 1200     | 3601              | 540           | 1081              | 144           | 289               |

| 1152     | 3458              | 480           | 962               | 120           | 244               |

| 1080     | 2160              | 432           | 864               | 108           | 221               |

| 972      | 3891              | 384           | 770               | 96            | 200               |

| 960      | 2881              | 360           | 721               | 72            | 149               |

| 900      | 1801              | 324           | 651               | 60            | 124               |

<sup>&</sup>lt;sup>2</sup> J. Greg Nash, "High-Throughput Programmable Systolic Array

FFT Architecture and FPGA Implementations", Presented at the 2014 International Conference on Computing, Networking and Communications (ICNC), Honolulu, HI, Feb 2014.

| 864 | 1728 | 300 | 601 | 48 | 102 |

|-----|------|-----|-----|----|-----|

| 768 | 2304 | 288 | 578 | 36 | 36  |

| 720 | 1440 | 240 | 481 | 24 | 24  |

| 648 | 1296 | 216 | 437 | 12 | 12  |

| 600 | 1201 | 192 | 384 |    |     |

#### **Performance and Resources**

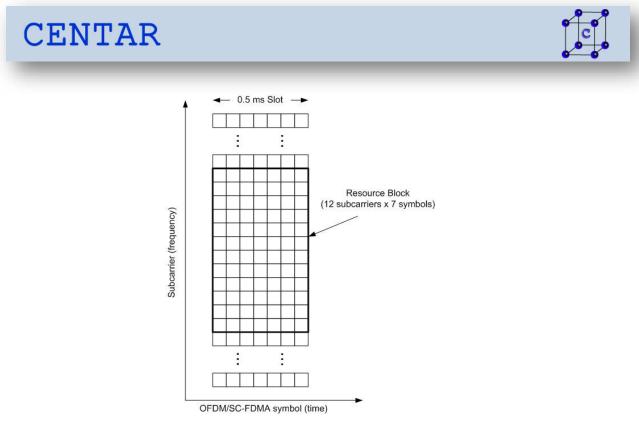

Here Centar's LTE SC-FDMA circuit is compared to commercial designs also implemented in FPGA technologies. In order to provide a more relevant metric than throughput and latency numbers the length of time necessary to compute an LTE resource block (RB), as shown diagrammatically in Fig.5, was chosen. The RB is the minimum processing unit of data for the LTE protocol and occupies one time "slot" (0.5ms), divided up into 7 symbols for (normal cyclic prefix). For example, 1296 subcarriers would imply processing a maximum of 108 RBs. This is a better performance comparison metric in that it requires both low latency and high throughput for good results.

#### Xilinx

A Vertix-6 (XC6VLX75T-3) FPGA was used as the target hardware for both the Xilinx and Centar's circuit. The same software tools (ISE 14.7) for synthesis and place-and-route were also used. The Xilinx LogiCORE IP version 3.1 was used to generate a 16-bit version of their DFT because the SQNR of 60.0 db (average over all 35 transform sizes) was comparable to Centar's 12-bit circuit with average SQNR=61.3. (Xilinx LogiCORE includes a bit accurate C model, callable as a Matlab mex function, that was used to obtain Xilinx SQNR values.)

The resource comparisons in the table below use a block RAM normalized to 18K bits, so that a 36K block RAM is considered equal to two 18K RAMs. Also, the "RB Average Throughput" column provides the average number of cycles (over all 35 DFT sizes) it takes to compute the DFT for the 7 symbols defined by a RB as a function of the transform size *N*. Finally, the Fmax (maximum clock frequency) value and the number of RB clock cycles are combined, providing a measure of the throughput, which is normalized to a value of "1" for the Centar design (a higher number is better). So the table shows the Xilinx circuit uses 66% more registers and 32% LUTs, while Centar circuits provides 41% higher throughput. So the overall combined gain is significant.

Fig. 5. LTE Resource block definition

The Centar design uses more embedded memory and multipliers, but this was less a consideration as discussed in Section I. Also, since many wireless applications involve use of MIMO and cell towers can have three different sectors operating simultaneously, it is possible that more than one single carrier DFT cores could be required. In theory Centar's 41% higher throughputs translate to fewer cores, which reduces considerably the Xilinx advantage in block RAM usage shown in the table.

#### Intel

Intel does not offer a DFT LTE core as does Xilinx; however, they have published results of an example design running on a Stratix III FPGA with 9K memory blocks that provides a useful basis for comparison.

For comparison the Centar design was also targeted to a Stratix III FPGA (EP3SE110F780C2) and the same Intel Quartus tools for synthesis and place-and-route were used to implement the design. The Intel implementation uses less logic, but is far slower, both in terms of the lower values of Fmax, and the increased number of cycles to complete the RB computation. Consequently, the Centar design has a significant  $\sim$ 3x higher throughput while LUT usage is only  $\sim$ 47% higher.

Note as well the Intel core doesn't offer a 1296-point transform option and the outputs are not in normal order. Adding buffer circuitry to sort the output data would require additional logic and add ~N additional words of memory (~5 9K RAM blocks) to the numbers shown in the table.

| Design     | FPGA        | LUT  | Registers | Block<br>RAM<br>(9/18K) | Multipliers<br>(18-bit) |     | RB<br>Average<br>Throughput<br>(cycles) | Throughput<br>(Normalized) |

|------------|-------------|------|-----------|-------------------------|-------------------------|-----|-----------------------------------------|----------------------------|

| Centar     | Virtex-6    | 2915 | 2581      | 19                      | 71                      | 401 | 16.6N                                   | 1                          |

| Xilinx [1] | Virtex-6    | 3849 | 4326      | 10                      | 16                      | 403 | 23.4N                                   | 0.72                       |

| Centar     | Stratix III | 3816 | 3188      | 29                      | 60                      | 400 | 16.6N                                   | 1                          |

| Intel [2]  | Stratix III | 2600 | N/A.      | 17                      | 32                      | 260 | 32.9N                                   | 0.33                       |

To support several sectors with MIMO several Intel cores would need to be used. In this case only one or two Centar cores would be required, so that the Intel block RAM advantage would be nullified, as shown in the table below. Here, the ratios are shown for each of the elements, normalized to the design with the small resource requirement for a particular element. As can be seen, except for the case of having just one sector and no more than two MIMO streams, the Centar design uses significantly fewer LUTs and block RAMs, and slightly fewer multipliers.

| Number<br>MIMO<br>Streams | Sectors | Total<br>RB | Intel<br>Cores<br>Required | Centar<br>Cores<br>Required | LUT<br>Intel::Centar | Block RAM<br>Intel::Centar | Multipliers<br>Intel::Centar |

|---------------------------|---------|-------------|----------------------------|-----------------------------|----------------------|----------------------------|------------------------------|

| 1                         | 1       | 1           | 1                          | 1                           | 1.00::1.47           | 1.00::1.32                 | 1.00::1.875                  |

| 2                         | 1       | 2           | 1                          | 1                           | 1.00::1.47           | 1.00::1.32                 | 1.00::1.875                  |

| 4                         | 1       | 4           | 2                          | 1                           | 1.36::1.00           | 1.52::1.00                 | 1.07::1.00                   |

| 1                         | 3       | 3           | 2                          | 1                           | 1.36::1.00           | 1.52::1.00                 | 1.07::1.00                   |

| 2                         | 3       | 6           | 3                          | 1                           | 2.04::1.00           | 2.27:1.00                  | 1.60::1.00                   |

| 4                         | 3       | 12          | 4                          | 2                           | 1.36::1.00           | 1.52::1.00                 | 1.07::1.00                   |

Operation as high as 450MHz has been verified using an Intel Stratix III development kit, which included an EP3SL150F1152C2 FPGA.

## **Device Family Support**

Intel Device Families Supported

- Stratix

- Aria

- Cyclone

# CENTAR

Hardcopy

## **Xilinx Device Families Supported**

- Virtex 4-7

- Spartan

- Artix-7

## Deliverables

- Netlist (e.g., for Intel FPGAs a verilog \*.qxp file for synthesis or \*.vo or lib file for simulation)

- Synthesis constraints (e.g., for Intel FPGA's an \*.sdc file)

- Modelsim LTE SC-FDMA Testbench (\*.vo or lib file for DFT circuit plus verilog testbench control file) that reads data from input file and outputs transform data to output file. Also includes Matlab verification utilities

- Quartus LTE SC-FDMA Test benches (35 DFT sizes, 12-points to 1296-points) that include pin-outs for use with an Intel Stratix III FPGA board development kit

- 1. On-chip input/output data memories and a \*.qxp file for the DFT circuit, that performs user selected number of blocks for a single size DFT

- On-chip input/output data memories, verilog control circuitry, and a \*.qxp file for the DFT circuit that cycles continuously through 2 blocks each of the LTE 35 different DFT sizes

- 3. Modelsim simulation environment of (2) using \*.vo file.

- Matlab behavioral bit-accurate model (p-code) for LTE SC-FDMA DFT sizes

- Documentation for above

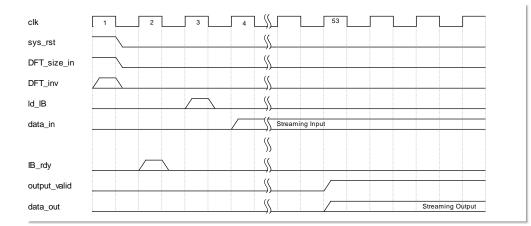

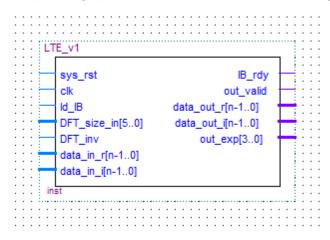

## Pin-outs

A symbol list corresponding to the pin-outs shown below are provided in the accompanying table. These apply to the "nominal variable" FFT circuit. For example some of the test benches do not include data I/O. Depending upon the desired interfaces, other signals could change.

| Name         | Signal                   | Description                                    |

|--------------|--------------------------|------------------------------------------------|

| clk_IO_in    | clock                    | Can be either a low frequency board oscillator |

|              |                          | clock output in which case circuit clock is    |

|              |                          | derived from a PLL or actual data I/O clock    |

| sys_rst      | control                  | Resets circuit; active high                    |

| DFT_size_in  | control; 5-bits unsigned | Registers DFT size                             |

| DFT_inv      | control                  | Low->forward; high->inverse                    |

| data_in_r/i  | n-bit signed             | Real and imaginary inputs; signed fixed-point  |

| IB_rdy       | control                  | Input buffer ready for data                    |

| out_valid    | control                  |                                                |

| out_exp      | 4-bits unsigned data     | Exponents (one per real/imag data pair)        |

| data_out_r/i | n-bit signed data        | Real and imaginary mantissa outputs            |

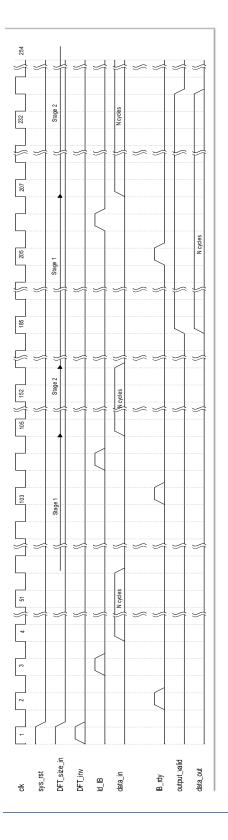

## **Timing Diagram**

A variety of timing possibilities exist depending upon the desired interface. That shown here is applicable to an example 48-point DFT, but other sizes will have the same form.

When  $sys\_rst$  goes high, the size and direction of the transform are latched. After the circuit generates  $IB\_rdy$ , the external data source generates  $Id\_IB$ , and on the next clock cycle the circuit expects to see *N* data values on the next *N* cycles. Valid data out occurs when *output\_valid* goes high:

CENTAR

For small DFTs, e.g., 12/24/36 points in the LTE protocol, streaming I/O is performed (continuous input and output) and the timing diagram is (for 12 points):